# DTX2-5055C

### mSPI RAM Drive

## **DATA SHEET**

#### TO OUR VALUED CUSTOMERS

It is a rule for us to try to provide our valued customers with the best documentation possible to ensure the successful implementation and use of our products. We will continue to improve our documentation to provide you with the maximum for your needs.

To obtain the most recent version of this data sheet, please visit our web site at <a href="http://www.dimitech.com">http://www.dimitech.com</a> or contact as at one of our publicly available email addresses.

You can determine the version of a data sheet by checking its version number found on the bottom left corner of the front page.

Every effort is made to verify the accuracy of information provided in this document, but no representation or warranty can be given and no liability assumed by Dimitech with respect to the accuracy and/or use of any products or information described in this document.

Any other products or information, subject to patents or innovations and mentioned in this data sheet are property to their lawful owners.

Dimitech will not be responsible for any patent infringements arising from the use of these products or information, and does not authorise or warrant the use of any of its products in life support devices without an explicit and official written permission.

Dimitech reserves the right to introduce changes to this document as well as the device(s) that it describes.

© 5/2013 Dimitech Pty Ltd, Document Version 4

DTX2-5055C 1/10

### 1. Overview

### Feature Highlights

- 68-pin device in standard PLCC68 package; three possible ways of mounting

- Wide range 4-20V DC power supply

- Fully self-contained does not need any external components to run

- Functionality implemented in hard logic for maximum operation speed

- Optional RAM retention power input with automatic switching between power supplies

- Activity LED on board

- RoHS compliant

### **Typical Applications**

- Temporary data storage

- OS swap memory

### **Ordering Codes**

| Device     | RAM size     |  |  |  |

|------------|--------------|--|--|--|

| DTX2-5055C | 16 Megabytes |  |  |  |

DTX2-5055C 2 / 10

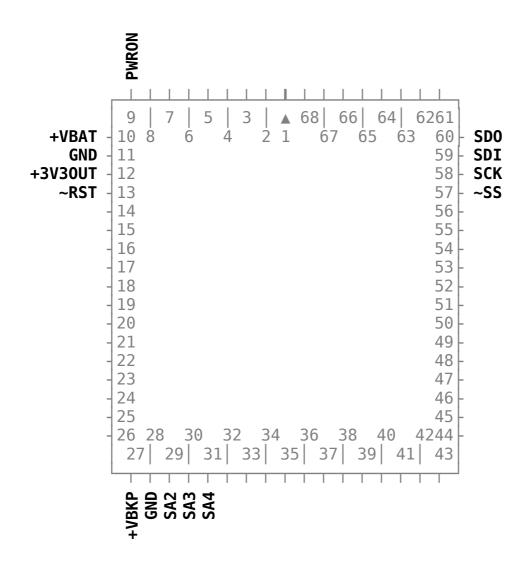

### 2. Pinout

### **Pinout Summary**

| Pin | Name | Туре | Description   |

|-----|------|------|---------------|

| 1   |      |      | No connection |

| 2   |      |      | No connection |

| 3   |      |      | No connection |

| 4   |      |      | No connection |

| 5   |      |      | No connection |

| 6   |      |      | No connection |

| 7   |      |      | No connection |

| 8   |      |      | No connection |

DTX2-5055C 3 / 10

| 9  | PWRON   | I | Power enabling input (can be connected directly to +VBAT); active high                                                                                         |

|----|---------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 | +VBAT   | Р | Positive power lead                                                                                                                                            |

| 11 | GND     | Р | Ground                                                                                                                                                         |

| 12 | +3V3OUT | Р | +3.3V output from the internal regulator                                                                                                                       |

| 13 | ~RST    | I | Resets the internal logic; RAM content remains unchanged; internally biased to +3.3V                                                                           |

| 14 |         |   | No connection                                                                                                                                                  |

| 15 |         |   | No connection                                                                                                                                                  |

| 16 |         |   | No connection                                                                                                                                                  |

| 17 |         |   | No connection                                                                                                                                                  |

| 18 |         |   | No connection                                                                                                                                                  |

| 19 |         |   | No connection                                                                                                                                                  |

| 20 |         |   | No connection                                                                                                                                                  |

| 21 |         |   | No connection                                                                                                                                                  |

| 22 |         |   | No connection                                                                                                                                                  |

| 23 |         |   | No connection                                                                                                                                                  |

| 24 |         |   | No connection                                                                                                                                                  |

| 25 |         |   | No connection                                                                                                                                                  |

| 26 |         |   | No connection                                                                                                                                                  |

| 27 | +VBKP   | Р | Backup power input (typically 3.3V); can charge an external supercapacitor or battery with approximately 3mA charging current; optional.  Leave open if unused |

| 28 | GND     | Р | Ground                                                                                                                                                         |

| 29 | SA2     | I | Serial address bit 2; see chapter "Operation" for more details                                                                                                 |

| 30 | SA3     | I | Serial address bit 3; see chapter "Operation" for more details                                                                                                 |

| 31 | SA4     | I | Serial address bit 4; see chapter "Operation" for more details                                                                                                 |

| 32 |         |   | No connection                                                                                                                                                  |

| 33 |         |   | No connection                                                                                                                                                  |

| 34 |         |   | No connection                                                                                                                                                  |

| 35 |         |   | No connection                                                                                                                                                  |

| 36 |         |   | No connection                                                                                                                                                  |

DTX2-5055C 4/10

| 37 |     |     | No connection                         |

|----|-----|-----|---------------------------------------|

| 38 |     |     | No connection                         |

| 39 |     |     | No connection                         |

| 40 |     |     | No connection                         |

| 41 |     |     | No connection                         |

| 42 |     |     | No connection                         |

| 43 |     |     | No connection                         |

| 44 |     |     | No connection                         |

| 45 |     |     | No connection                         |

| 46 |     |     | No connection                         |

| 47 |     |     | No connection                         |

| 48 |     |     | No connection                         |

| 49 |     |     | No connection                         |

| 50 |     |     | No connection                         |

| 51 |     |     | No connection                         |

| 52 |     |     | No connection                         |

| 53 |     |     | No connection                         |

| 54 |     |     | No connection                         |

| 55 |     |     | No connection                         |

| 56 |     |     | No connection                         |

| 57 | ~SS | I   | mSPI "Slave Select" input; active low |

| 58 | SCK | I   | mSPI clock                            |

| 59 | SDI | I   | mSPI serial data input                |

| 60 | SDO | O,Z | mSPI serial data output               |

| 61 |     |     | No connection                         |

| 62 |     |     | No connection                         |

| 63 |     |     | No connection                         |

| 64 |     |     | No connection                         |

| 65 |     |     | No connection                         |

| 66 |     |     | No connection                         |

| 67 |     |     | No connection                         |

| 68 |     |     | No connection                         |

**Legend:**I – input with CMOS level

A – analogue signal

S – special functionality

**O** – digital output **P** – power pin

E – open drain/collector outputZ – high impedance

5/10 DTX2-5055C

### 3. Electrical Parameters

#### **ABSOLUTE MAXIMUM RATINGS:**

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied.

Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

| parameter                                                     | min | typ                                                        | max | units |  |

|---------------------------------------------------------------|-----|------------------------------------------------------------|-----|-------|--|

| Power supply voltage range, pin +VBAT with respect to pin GND | 3.5 | 9                                                          | 20  | V     |  |

| Voltage on pin +VBKP with respect to pin GND                  | 2.5 | 3                                                          | 3.7 | V     |  |

| Safe load on +3V3OUT pin                                      |     |                                                            | 200 | mA    |  |

| Current drain from +VBKP in backup mode                       |     | 0.4                                                        | 33  | mA    |  |

| Parameters of all other functional pins                       |     | According to function and IC manufacturer's recommendation |     |       |  |

| Operating free-air temperature range                          | -20 |                                                            | +85 | °C    |  |

| Storage temperature range                                     | -40 |                                                            | +90 | °C    |  |

## 4. Dynamic Parameters

#### **PRELIMINARY DETAILS:**

The following details are preliminary and based on calculated results and not fully tested. They are incomplete and some inaccuracies are also possible. Use with caution!

| parameter                              | min  | typ | max | units |

|----------------------------------------|------|-----|-----|-------|

| ~RST active low time                   | 200  |     |     | nS    |

| SCK input clock frequency <sup>1</sup> | 0.15 | 20  | 27  | MHz   |

|                                        |      |     |     |       |

|                                        |      |     |     |       |

|                                        |      |     |     |       |

|                                        |      |     |     |       |

|                                        |      |     |     |       |

1. Assuming 50% duty cycle

DTX2-5055C 6/10

### 5. Internal Schematic

<u>Note:</u> Dimitech Pty Ltd reserves the rights to make further adjustments in this circuit without prior notifications

The internal circuit of DTX2-5055C is available as a separate document. Please refer to <a href="https://document.pdf">DTX2-5055C\_circuit.PDF</a>

### 6. Operation

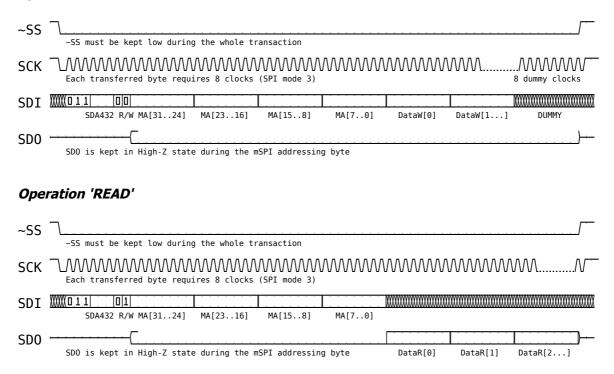

DTX2-5055C conforms with the basic mSPI protocol acting as a slave device.

On a hardware level the communication is done via SPI mode 3 with 3.3V signal levels (not 5V-tolerant). All bytes are transferred starting with bit 7 and ending with bit 0. Multi-byte sequences (such as the 32-bit memory address below) are transferred starting with the most significant byte and ending with the least significant byte.

As per the mSPI specification, the master device is required to address the slave in the bus within the first byte of every new data transaction.

The mSPI address byte is as follows:

#### Byte 0

| Г | 0     | 1     | 1     | SDA4  | SDA3  | SDA2  | 0     | R/W   |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

This is the very first byte which DTX2-5055C will be looking for at the start of every data transaction on the bus. If not addressed, DTX2-5055C will remain in standby mode.

Bits 7, 6, 5 and 1 in the address byte have constant pre-set values (0, 1, 1 and 0 respectively).

Bits 4, 3 and 2 are taken from the SDA4, SDA3 and SDA2 inputs, thus forming eight possible address configurations.

The default value of all SDAx bits is 1 (if left unconnected) thus defining the default mSPI address of DTX2-5055C to be 0x7c.

The last bit 0 specifies operation **Read/Write** with the memory. If it has value 0, DTX2-5055C will read the incoming data and write it into the memory. If the value of bit 0 is 1, data will be read and sent to the master until the end of the data transaction. **Utilising this addressing model DTX2-5055C occupies two default mSPI addresses: 0x7c for writing, and 0x7d for reading.**

By changing the values of SDAx bytes other mSPI address pairs can be formed in case more than one DTX2-5055C devices are used in a bus.

DTX2-5055C 7/10

Following the addressing byte, the master is required to issue memory start address for the data transaction. DTX2-5055C reads fixed number of four memory address bytes, which form a 32-bit memory address. Assuming the mSPI address byte is numbered as "byte 0", the following four received bytes are forming the memory address:

| Rvta | 1 |

|------|---|

| שועם | _ |

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MA31  | MA30  | MA29  | MA28  | MA27  | MA26  | MA25  | MA24  |

#### Byte 2

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MA23  | MA22  | MA21  | MA20  | MA19  | MA18  | MA17  | MA16  |

#### Byte 3

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MA15  | MA14  | MA13  | MA12  | MA11  | MA10  | MA9   | MA8   |

#### Byte 4

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MA7   | MA6   | MA5   | MA4   | MA3   | MA2   | MA1   | MA0   |

DTX2-5055C implements 16 Megabytes of data memory, which is addressed using the MA0-MA23 bits.

MA24-MA31 have no meaning and should be kept always 0.

After supplying the five addressing bytes (mSPI address and 32-bit memory address), the master device can now start clocking in or clocking out data bytes, depending on the operation Read or Write.

DTX2-5055C uses burst mode in order to create maximum memory utilisation when working with sequential memory addresses. After every data byte the address, initially supplied by the master device in MA31-MA0 is incremented by 1. This will be continuously done until ~SS is kept in active low and the device is addressed.

Using burst mode in essence means that the master can supply one starting memory address and then keep sending or receiving data starting from that address onwards for as long as DTX2-5055C is kept active active. Thus reading or writing a continuous data block requires the master to send the starting address of the block only once at the beginning of the data transaction and then transfer the whole data block at once.

**Important!** When executing a <u>write</u> transaction, the master device is required to clock one additional "dummy" byte before the end of the transaction. SDO and SDI lines carry no meaningful data during the transfer of this dummy byte.

DTX2-5055C 8 / 10

The communication as described is shown in the pictures below.

#### Operation 'WRITE'

DTX2-5055C 9/10

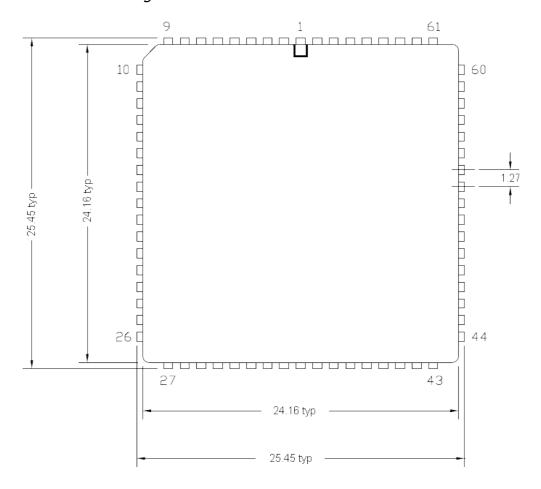

## 7. Mechanical Parameters

Note: All dimensions are given in millimetres

**Dimitech Pty Ltd** provides CAD schematic symbols and PCB footprints for the DTX series modules. For more information please visit our website: <a href="http://www.dimitech.com/">http://www.dimitech.com/</a>.

DTX2-5055C